معماری ARM چیست و چه تفاوتی با x86 اینتل دارد؟

امروزه هر جا صحبت از تلفن هوشمند یا تبلت به میان میآید، حتما نام ARM نیز به گوش میرسد. پردازنده اکثر تبلت و تلفنهای هوشمند بازار مبتنی بر معماری ARM است. اما ARM به چه معناست؟ معماری ARM چیست؟ چه تفاوتی با x86 اینتل میکند؟ چرا این معماری تا به این اندازه محبوب شده و دنیای موبایل را تحت کنترل خود قرار داده است؟ در ادامه مطلب برای رسیدن به پاسخ این پرسشها با هارد ویر وی سنتر همراه باشید.

{autotoc}در این مقاله به معرفی ARM، تاریخچه آن و بررسی کلی نسلهای مختلف CPUهای ARM میپردازیم اما در آینده نسلهای پردازندههای ARM را با یکدیگر مقایسه نموده و توضیحات کاملی در مورد هر نسل ارائه خواهیم کرد.

تاریخچه ARM

ARM نوعی از معماری پردازندههای کامپیوتری است که بر طبق طراحی RISC CPU و توسط کمپانی بریتانیاییARM Holding طراحی شده است. معماری ARM که دستورالعملهای 32 بیتی را پردازش میکند از دهه 1980 تا به امروز در حال توسعه است.

ARM مخفف Advanced RISC Machine است و از آنجایی که این معماری براساس طراحی RISC بنا شده، هسته اصلی CPU نیاز به 35 هزار ترانزیستور دارد این در حالی است که پردازندههای معمولی رایج x86 که براساس CISC طراحی شدهاند حداقل نیاز به میلیونها ترانزیستور دارند. مهمترین دلیل مصرف بسیار پایین انرژی در پردازندههای مبتنی بر ARM که باعث استفاده گسترده آنها در ابزارهای پرتابل مانند تلفن هوشمند یا تبلت شده نیز همین موضوع است.

جالب است بدانید که شرکت ARM Holding خود تولیدکننده پردازنده نیست و در عوض گواهی استفاده از معماری ARM را به دیگر تولیدکنندگان نیمه هادی میفروشد. کمپانیها نیز به راحتی تراشههای خود را براساس معماری ARM تولید میکنند. از جمله کمپانیهایی که پردازنده خود را براساس معماری ARM طراحی میکنند میتوان به اپل در تراشههای Ax، سامسونگ در پردازندههای Exynos، انویدیا در تگرا و کوالکام در پردازندههای Snpdragon اشاره کرد.

در سال 2011 مشتریان ARM توانستند 7.9 میلیارد ابزار مبتنی بر این معماری را وارد بازار کنند. شاید تصور میکنید که پردازندههای مبتنی بر ARM تنها در تبلت و تلفنهای هوشمند بکار گرفته میشوند، اما جالب است بدانید که در همین سال بیش از 95 درصد تلفنهای هوشمند دنیا، 90 درصد دیسکهای سخت (HDD)، حدود 40 درصد تلویزیونهای دیجیتال و ستتاپباکسها، 15 درصد میکروکنترلرها و 20 درصد کامپیوترهای موبایل مجهز به پردازندههای مبتنی بر معماری ARM بودهاند. بدون شک این آمار در سال 2012 رشد فوقالعاده چشم گیری را تجربه کرده است، چون بازار تلفنهای هوشمند و تبلتهای در سال جاری پیشرفت قابل ملاحظهای داشتهاند.

تا اینجای کار معماری ARM تنها برروی پلتفرم 32 بیتی با عرض حافظه 1 بایت کار میکرد. اما با معرفی ARMv8 این معماری پشتیبانی از دستورات 64 بیتی را نیز آغاز کرد که البته هنوز در سیستم-روی-یک-چیپها بکار گرفته نشده است. در سال 2012 مایکروسافت نیز نسخه ویندوز سازگار با معماری ARM را به همراه تبلت سرفیس RTمعرفی کرد. AMD نیز اعلام نموده که قصد دارد در سال 2014 سرورهای مبتنی بر معماری 64 بیتی ARM را روانه بازار کند.

همانطور که پیشتر اشاره کردیم، ARM گواهی استفاده از معماری خود را به شرکتهای دیگر میدهد، کمپانیهایی که در حال حاضر گواهی استفاده از ARM را دارند عبارتند از: AMD, آلکاتل, اپل, AppliedMicro, Atmel, Broadcom, Cirrus Logic, CSR plc, Digital Equipment Corporation, Ember, Energy Micro, Freescale, فوجیتسو, Fuzhou Rockchip, هواوی, اینتل توسط شرکتهای زیر شاخه, ال جی, Marvell Technology Group, Microsemi, مایکروسافت, NEC, نینتندو, Nuvoton, انویدیا, NXP (formerly Philips Semiconductor), Oki, ON Semiconductor, پاناسونیک, کوالکام, Renesas, Research In Motion, سامسونگ, شارپ, Silicon Labs, سونی, اریکسون, STMicroelectronics, Symbios Logic, Texas Instruments, توشیبا, یاماها و ZiiLABS

RISC و CISC یا ARM در مقابل x86

RISC که مخفف Reduced instruction Set Computing یا مجموعه دستورات ساده شده است در واقع نوعی از طراحی CPU است که پایه و اساس آن، ساده سازی دستورات است که منجر به بازده بالا و سرعت بخشیدن به اجرای دستورات میشود. پردازدهای که براساس این طراحی ساخته میشود را RISC (بخوانید ریسک) مینامند. مهمترین و معروفترین معماری که براساس RISC طراحی شده، ARM است. درست نقطه مقابل ریسک، طراحی دیگری با نام CISC وجود دارد که مخفف Complex Instruction Set Computing یا مجموعه دستورات پیچیده است که معماری x86 اینتل براساس آن طراحی شده و پردازنده کامپیوترهای رومیزی و لپ تاپها و بسیاری از ابزارهای دیگر از آن بهره میبرند.

ایده اصلی RISC اولین بار توسط جان کوکی از IBM و در سال 1974 شکل گرفت، نظریه او به این موضوع اشاره داشت که یک کامپیوتر تنها از 20 درصد از دستورات نیاز دارد و 80 درصد دیگر، دستورات غیرضروری هستند. پردازندههای ساخته شده براساس این طراحی از دستورات کمی پشتیبانی میکنند به این ترتیب به ترانزیستور کمتری نیز نیاز دارند و ساخت آنها نیز کم هزینه است. با کاهش تعداد ترانزیستورها و اجرای دستورات کمتر، پردازنده در زمان کمتری دستورات را پردازش میکند. کمی بعد اصطلاح RISC توسط یک استاد دانشگاه کالیفورنیا به نام دیوید پترسون ایجاد شد.

هر دو طراحی RISC و CISC به مراتب در انواع و اقسام ابزارها بکار گرفته میشوند، اما مفهوم کلی RISC در واقع سیستمی است که در آن به پردازش دستورات کوچک و به شدت بهینه شده پرداخته میشود، درست برخلاف CISC که در آن دستورات پیچیده ارسال میشوند. یکی از تفاوتهای عمده بین RISC و CISC نیز در نحوه دسترسی به حافظه و ذخیره و اجرای اطلاعات برروی آن است. در ریسک دسترسی به حافظه تنها از طریق دستورالعملهای خاصلی قابل انجام است و به عنوان مثال نمیتوان از بخشی از دستور add به حافظه دسترسی داشت.

علاوه بر ARM شرکتهای بسیار دیگری از جمله Intel i860, AMD 29k, ARC و غیره از طراحی RISC برای ساخت پردازنده استفاده میکنند، اما به لطف گسترش تلفن و تبلتها، معماری ARM به عنوان برجستهترین معماری مبتنی بر RISC شناخته میشود.

CISC

در سیسک اوضاع دقیقا برعکس ریسک است و پردازنده قادر به پردازش دستورات پیچیده است به همین دلیل نیاز به تعداد بیشتر ترانزیستور و همچنین طراحی پیچیدهتر و پردازندههای گران قیمتتر دارد. ایده اصلی پشت این طراحی این است که برنامه نویسان سادهتر بتوانند نرم افزارهای خود را تولید کنند و دستورات را سادهتر به CPU ارجاع دهند. به لطف پشتیبانی اینتل و تولیدکنندگان نرم افزار، CISC به شدت محبوب شد و تمام کامپیوترها از پردازنده مبتنی بر این طراحی بهره بردند.

برخی تصور میکنند که ریسک قادر به اجرای دستورات زیاد نیست اما در حقیقت ریسک به اندازه سیسک میتواند دستورات مختلف را اجرا کند اما مهمترین تفاوت این دو در این است که در RISC تمام دستورات با یک فرمت، دقیقا یک فرمت صادر میشوند و پردازش تمام دستورات یک زمان مشخص طول میکشد، معمولا در ریسک در هر سیکل، پردازنده یک دستور را اجرا میکند.

اما در CISC مجموعهای از دستورات بصورت فشرده و با آدرس دهی مختلف به یکباره پردازش میشوند، مثل اعداد اعشاری یا تقسیم که در طراحی RISC وجود ندارند. از آنجایی که دستورات در RISC سادهتر هستند پس سریعتر اجرا میشوند و نیاز به ترانزیستور کمتری دارند، ترانزیستور کمتر هم به معنی دمای کمتر، مصرف پایینتر و فضای کمتر است که آن را برای ابزارهای موبایل مناسب میکند.

معماری پردازندههای مبتنی بر طراحی RISC طی سالهای گذشته پیشرفت چشمگیری داشته و اجرای دستورات پیچیده را نیز میسر کرده است و تولیدکنندگان نرم افزاری نیز به سمت ساخت نرمافزارهای مبتنی بر این معماری گرایش پیدا کردهاند. لازم است بدانید که کامپیوترهای اولیه مک نیز از پردازنده مبتنی بر RISC بهره میبردند.

اما در واقع پردازندههای CISC بسیار سریعتر و پرقدرتتر از RISCها هستند و قادر به پردازش امور سنگین میباشند اما در عوض گرانقیمتتر، پرمصرفتر بوده و دمای بیشتری نیز تولید میکنند. در CISC تمرکز برروی سختافزار است و در RISC برروی نرمافزار، در CISC دستورات بصورت پیچیده به پردازنده ارسال میشوند ولی در RISC نرمافزار دستورات را ساده کرده و به عنوان مثال یک عملیات پیچیده را در قالب چندین دستور ساده به پردازنده ارسال میکند و پردازنده دستورات ساده را به سرعت پردازش نموده و نتیجه را باز میگرداند. پس کدهای نرمافزارهای سازگار با RISC طولانی تر ولی کدهای مربوط به نرمافزارهای CISC کوتاهتر و پیچیدهتر هستند. البته این بدین معنا نیست که مثلا اگر قرار است برای اندروید یا iOS برنامه بنویسید باید چند هزار خط بیشتر از معادل کامپیوتر ویندوزی آن کد نویسی کنید، در واقع کامپایلرها کدها را به دستورات کوچک زیاد تبدیل میکنند و برنامه نویس به سختی متوجه نوع پردازش دستورات میشود.

اگر بخواهیم در مورد این دو طراحی صحبت کنیم بحث پیچیده و کسل کننده خواهد شد پس به همین جا بسنده میکنیم اما اگر تمایل دارید تا در مورد این طراحیها بیشتر بدانید به این دو لینک مراجعه کنید: CISC و RISC

سیستم-روی-یک-چیپها و معماری ARM

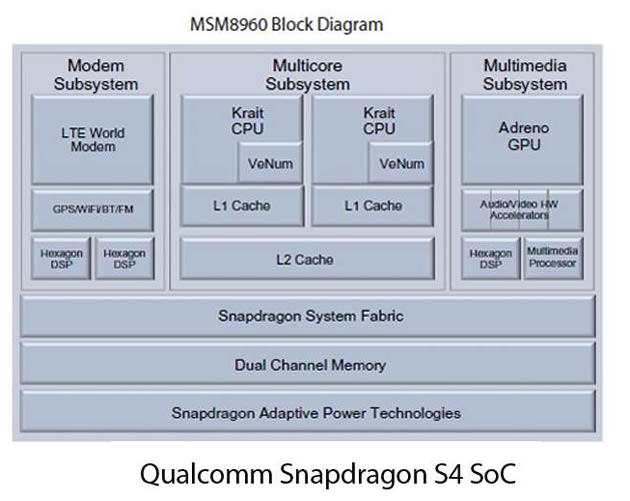

چندین نوع مختلف از معماری برای پردازندههای ARM وجود دارد که از آن جمله میتوان به ARM V2 ،ARMv3 Arm v7 و …اشاره کرد. کمپانیها برای استفاده از هر کدام از این طراحیها باید گواهی مربوط به آن را از ARM Holder دریافت کنند. کمپانیها از این معماری در ساخت پردازنده های مورد نظر خود بهره برده و در نهایت یا یکپارچه سازی آن با واحد پردازش گرفیک (GPU)، حافظه رم و قسمت کنترلر باند رادیویی (در تلفنهای هوشمند) سیستم -روی-یک-چیپ خود را می سازند .

سیستم-روی-یک-چیپ (System on a Chip) که آن را به اختصار SoC مینامند در واقع یک تراشه است که در آن پردازنده اصلی (CPU)، پردازنده گرافیک (GPU)، حافظه رم، کنترلرهای ورودی و خروجی و بعضا کنترلر باند رادیویی قرار دارند. پس لازم است بدانید که کل SoC براساس معماری ARM تولید نمیشود و تنها بخش CPU آن بر مبنای معماری ARM طراحی و تولید میگردد. پس این باور که فلان SoC براساس معماری ARM ساخته شده، اشتباه است و بخش پردازنده اصلی اکثر SoCها براساس یکی از طراحهای معماری ARM ساخته میشوند.

از جمله سیستم-روی-یک-چیپهایی که هسته اصلی آنها براساس معماری ARM طراحی شدهاند میتوان به 3 نسل اول تگرا انویدیا، Quatro شرکت CSRT، نوا شرکت اریکسون، OMAP شرکت تکزاس، Exynos شرکت سامسونگ و Ax شرکت اپل اشاره کرد. این شرکت ها از معماری ARM و همچنین معماری یکی از هستههای طراحی شده توسط این شرکت بهره بردهاند.

اما شرکتها میتوانند گواهی استفاده از معماری ARM را تهیه کرده و سپس بر اساس آن هسته سفارشی مورد نظرشان را طراحی کنند یعنی به جای اینکه هسته CPU را براساس Cortex-A9 یا Cortex-A15 یا دیگر هستههای ARM بسازنند، خودشان براساس معماری یکی از خانوادههای ARM، هسته خاص خود را طراحی کنند. به عنوان مثال سیستم-روی-یک-چیپ A6 اپل، X-Gene ،Krait کوالکام، StrongARM شرکت DEC ،XScale شرکت Marvell اینتل یا Project Denver شرکت انویدیا اینگونه هستند و اگر چه بخش CPU از سیستم-روی-یک-چیپ آنها براساس معماری ARM طراحی شدهاند، اما طراحی هستهها با آنچه ARM پیشنهاد کرده متفاوت هستند.

انواع مختلف هستههای مبتنی بر ARM

همانطور که پیشتر اشاره کردیم، شرکت ARM Holding خود نسبت به طراحی هسته براساس معماری ARM اقدام میکند و هستههای متفاوتی را براساس نسلهای مختلف این معماری عرضه کرده است، جدیدترین معماری این شرکت ARM v8 است که از دستورات 64 بیتی پشتیبانی میکند و دو هسته Cortex A53 و Cortex A57 نیز براساس همین معماری طراحی و پیشنهاد شدهاند. انتظار میرودی SoCهای سال آینده از این معماری بهره مند شوند، در جدول زیر کل هستههای طراحی شده توسط ARMرا مشاهده خواهید کرد:

| ARM Family | ARM Architecture | ARM Core | Feature | Cache (I/D), MMU | Typical MIPS @ MHz |

|---|---|---|---|---|---|

| ARM1 | ARMv1 | ARM1 | First implementation | None | |

| ARM2 | ARMv2 | ARM2 | ARMv2 added the MUL (multiply) instruction | None | 4 MIPS @ 8 MHz 0.33 DMIPS/MHz |

| ARMv2a | ARM250 | Integrated MEMC (MMU), Graphics and IO processor. ARMv2a added the SWP and SWPB (swap) instructions. | None, MEMC1a | 7 MIPS @ 12 MHz | |

| ARM3 | ARMv2a | ARM3 | First integrated memory cache. | 4 KB unified | 12 MIPS @ 25 MHz 0.50 DMIPS/MHz |

| ARM6 | ARMv3 | ARM60 | ARMv3 first to support 32-bit memory address space (previously 26-bit) | None | 10 MIPS @ 12 MHz |

| ARM600 | As ARM60, cache and coprocessor bus (for FPA10 floating-point unit). | 4 KB unified | 28 MIPS @ 33 MHz | ||

| ARM610 | As ARM60, cache, no coprocessor bus. | 4 KB unified | 17 MIPS @ 20 MHz 0.65 DMIPS/MHz |

||

| ARM7 | ARMv3 | ARM700 | 8 KB unified | 40 MHz | |

| ARM710 | As ARM700, no coprocessor bus. | 8 KB unified | 40 MHz | ||

| ARM710a | As ARM710 | 8 KB unified | 40 MHz 0.68 DMIPS/MHz |

||

| ARM7TDMI | ARMv4T | ARM7TDMI(-S) | 3-stage pipeline, Thumb | none | 15 MIPS @ 16.8 MHz 63 DMIPS @ 70 MHz |

| ARM710T | As ARM7TDMI, cache | 8 KB unified, MMU | 36 MIPS @ 40 MHz | ||

| ARM720T | As ARM7TDMI, cache | 8 KB unified, MMU with Fast Context Switch Extension | 60 MIPS @ 59.8 MHz | ||

| ARM740T | As ARM7TDMI, cache | MPU | |||

| ARM7EJ | ARMv5TEJ | ARM7EJ-S | 5-stage pipeline, Thumb, Jazelle DBX, Enhanced DSP instructions | none | |

| ARM8 | ARMv4 | ARM810[4][5] | 5-stage pipeline, static branch prediction, double-bandwidth memory | 8 KB unified, MMU | 84 MIPS @ 72 MHz 1.16 DMIPS/MHz |

| ARM9TDMI | ARMv4T | ARM9TDMI | 5-stage pipeline, Thumb | none | |

| ARM920T | As ARM9TDMI, cache | 16 KB/16 KB, MMU with FCSE (Fast Context Switch Extension)[6] | 200 MIPS @ 180 MHz | ||

| ARM922T | As ARM9TDMI, caches | 8 KB/8 KB, MMU | |||

| ARM940T | As ARM9TDMI, caches | 4 KB/4 KB, MPU | |||

| ARM9E | ARMv5TE | ARM946E-S | Thumb, Enhanced DSP instructions, caches | variable, tightly coupled memories, MPU | |

| ARM966E-S | Thumb, Enhanced DSP instructions | no cache, TCMs | |||

| ARM968E-S | As ARM966E-S | no cache, TCMs | |||

| ARMv5TEJ | ARM926EJ-S | Thumb, Jazelle DBX, Enhanced DSP instructions | variable, TCMs, MMU | 220 MIPS @ 200 MHz | |

| ARMv5TE | ARM996HS | Clockless processor, as ARM966E-S | no caches, TCMs, MPU | ||

| ARM10E | ARMv5TE | ARM1020E | 6-stage pipeline, Thumb, Enhanced DSP instructions, (VFP) | 32 KB/32 KB, MMU | |

| ARM1022E | As ARM1020E | 16 KB/16 KB, MMU | |||

| ARMv5TEJ | ARM1026EJ-S | Thumb, Jazelle DBX, Enhanced DSP instructions, (VFP) | variable, MMU or MPU | ||

| ARM11 | ARMv6 | ARM1136J(F)-S[7] | 8-stage pipeline, SIMD, Thumb, Jazelle DBX, (VFP), Enhanced DSP instructions | variable, MMU | 740 @ 532–665 MHz (i.MX31 SoC), 400–528 MHz |

| ARMv6T2 | ARM1156T2(F)-S | 8-stage pipeline, SIMD, Thumb-2, (VFP), Enhanced DSP instructions | variable, MPU | ||

| ARMv6Z | ARM1176JZ(F)-S | As ARM1136EJ(F)-S | variable, MMU + TrustZone | 965 DMIPS @ 772 MHz, up to 2 600 DMIPS with four processors[8] | |

| ARMv6K | ARM11 MPCore | As ARM1136EJ(F)-S, 1–4 core SMP | variable, MMU | ||

| SecureCore | ARMv6-M | SC000 | 0.9 DMIPS/MHz | ||

| ARMv4T | SC100 | ||||

| ARMv7-M | SC300 | 1.25 DMIPS/MHz | |||

| Cortex-M | ARMv6-M | Cortex-M0 [9] | Microcontroller profile, Thumb + Thumb-2 subset (BL, MRS, MSR, ISB, DSB, DMB),[10]hardware multiply instruction (optional small), optional system timer, optional bit-banding memory | No cache, No TCM, No MPU | 0.84 DMIPS/MHz |

| Cortex-M0+ [11] | Microcontroller profile, Thumb + Thumb-2 subset (BL, MRS, MSR, ISB, DSB, DMB),[10]hardware multiply instruction (optional small), optional system timer, optional bit-banding memory | No cache, No TCM, optional MPU with 8 regions | 0.93 DMIPS/MHz | ||

| Cortex-M1 [12] | Microcontroller profile, Thumb + Thumb-2 subset (BL, MRS, MSR, ISB, DSB, DMB),[10]hardware multiply instruction (optional small), OS option adds SVC / banked stack pointer, optional system timer, no bit-banding memory | No cache, 0-1024 KB I-TCM, 0-1024 KB D-TCM, No MPU | 136 DMIPS @ 170 MHz,[13] (0.8 DMIPS/MHz FPGA-dependent)[14] | ||

| ARMv7-M | Cortex-M3 [15] | Microcontroller profile, Thumb / Thumb-2, hardware multiply and divide instructions, optional bit-banding memory | No cache, No TCM, optional MPU with 8 regions | 1.25 DMIPS/MHz | |

| ARMv7E-M | Cortex-M4 [16] | Microcontroller profile, Thumb / Thumb-2 / DSP / optional FPv4 single-precision FPU, hardware multiply and divide instructions, optional bit-banding memory | No cache, No TCM, optional MPU with 8 regions | 1.25 DMIPS/MHz | |

| Cortex-R | ARMv7-R | Cortex-R4 [17] | Real-time profile, Thumb / Thumb-2 / DSP / optional VFPv3 FPU, hardware multiply and optional divide instructions, optional parity & ECC for internal buses / cache / TCM, 8-stage pipeline dual-core running lockstep with fault logic | 0-64 KB / 0-64 KB, 0-2 of 0-8 MB TCM, opt MPU with 8/12 regions | |

| Cortex-R5 (MPCore) [18] | Real-time profile, Thumb / Thumb-2 / DSP / optional VFPv3 FPU and precision, hardware multiply and optional divide instructions, optional parity & ECC for internal buses / cache / TCM, 8-stage pipeline dual-core running lock-step with fault logic / optional as 2 independent cores, low-latency peripheral port (LLPP), accelerator coherency port (ACP) [19] | 0-64 KB / 0-64 KB, 0-2 of 0-8 MB TCM, opt MPU with 12/16 regions | |||

| Cortex-R7 (MPCore) [20] | Real-time profile, Thumb / Thumb-2 / DSP / optional VFPv3 FPU and precision, hardware multiply and optional divide instructions, optional parity & ECC for internal buses / cache / TCM, 11-stage pipeline dual-core running lock-step with fault logic / out-of-order execution / dynamic register renaming / optional as 2 independent cores, low-latency peripheral port (LLPP), ACP [19] | 0-64 KB / 0-64 KB, ? of 0-128 KB TCM, opt MPU with 16 regions | |||

| Cortex-A | ARMv7-A | Cortex-A5 [21] | Application profile, ARM / Thumb / Thumb-2 / DSP / SIMD / Optional VFPv4-D16 FPU / Optional NEON / Jazelle RCT and DBX, 1–4 cores / optional MPCore, snoop control unit (SCU), generic interrupt controller (GIC), accelerator coherence port (ACP) | 4-64 KB / 4-64 KB L1, MMU + TrustZone | 1.57 DMIPS / MHz per core |

| Cortex-A7 MPCore [22] | Application profile, ARM / Thumb / Thumb-2 / DSP / VFPv4-D16 FPU / NEON / Jazelle RCT and DBX / Hardware virtualization, in-order execution, superscalar, 1–4 SMP cores, Large Physical Address Extensions (LPAE), snoop control unit (SCU), generic interrupt controller (GIC), ACP, architecture and feature set are identical to A15, 8-10 stage pipeline, low-power design[23] | 32 KB / 32 KB L1, 0-4 MB L2, L1 & L2 have Parity & ECC, MMU + TrustZone | 1.9 DMIPS / MHz per core | ||

| Cortex-A8 [24] | Application profile, ARM / Thumb / Thumb-2 / VFPv3 FPU / Optional NEON / Jazelle RCT and DAC, 13-stage superscalar pipeline | 16-32 KB / 16-32 KB L1, 0-1 MB L2 opt ECC, MMU + TrustZone | up to 2000 (2.0 DMIPS/MHz in speed from 600 MHz to greater than 1 GHz) | ||

| Cortex-A9 MPCore [25] | Application profile, ARM / Thumb / Thumb-2 / DSP / Optional VFPv3 FPU / Optional NEON / Jazelle RCT and DBX, out-of-order speculative issue superscalar, 1–4 SMP cores, snoop control unit (SCU), generic interrupt controller (GIC), accelerator coherence port (ACP) | 16-64 KB / 16-64 KB L1, 0-8 MB L2 opt Parity, MMU + TrustZone | 2.5 DMIPS/MHz per core, 10,000 DMIPS @ 2 GHz on Performance Optimized TSMC 40G (dual core) | ||

| Cortex-A15 MPCore [26] | Application profile, ARM / Thumb / Thumb-2 / DSP / VFPv4 FPU / NEON / Jazelle RCT / Hardware virtualization, out-of-order speculative issue superscalar, 1–4 SMP cores, Large Physical Address Extensions (LPAE), snoop control unit (SCU), generic interrupt controller (GIC), ACP, 15-24 stage pipeline[23] | 32 KB / 32 KB L1, 0-4 MB L2, L1 & L2 have Parity & ECC, MMU + TrustZone | At least 3.5 DMIPS/MHz per core (Up to 4.01 DMIPS/MHz depending on implementation).[27] | ||

| ARMv8-A | Cortex-A53[28] | Application profile, AArch32 and AArch64, 1-4 SMP cores, Trustzone, NEON advanced SIMD, VFPv4, hardware virtualization, dual issue, in-order pipeline | 8~64 KB/8~64 KB L1 per core, 128 KB~2 MB L2 shared, 40-bit physical addresses | 2.3 DMIPS/MHz | |

| Cortex-A57[29] | Application profile, AArch32 and AArch64, 1-4 SMP cores, Trustzone, NEON advanced SIMD, VFPv4, hardware virtualization, multi-issue, deeply out-of-order pipeline | 48 KB/32 KB L1 per core, 512 KB~2 MB L2 shared, 44-bit physical addresses | At least 4.1 DMIPS/MHz per core (Up to 4.76 DMIPS/MHz depending on implementation). | ||

| ARM Family | ARM Architecture | ARM Core | Feature | Cache (I/D), MMU | Typical MIPS @ MHz |

اما برخی از تولیدکنندگان مانند کوالکام، انویدیا یا اپل، طراحهای شرکت ARM Holding را قبول ندارند و خود نسبت به طراحی هسته سفارشی بر مبنای معماری ARM اقدام میکنند. در جدول زیر هستههای طراحی شده توسط شرکتهای دیگر که البته بر مبنای معماری یکی از خانودههای ARM هستند را مشاهده میکنید:

| Family | ARM Architecture | Core | Feature | Cache (I/D), MMU | Typical MIPS @ MHz |

|---|---|---|---|---|---|

| StrongARM | ARMv4 | SA-1 | 5-stage pipeline | 16 KB/8–16 KB, MMU | 203–206 MHz 1.0 DMIPS/MHz |

| XScale | ARMv5TE | XScale | 7-stage pipeline, Thumb, Enhanced DSP instructions | 32 KB/32 KB, MMU | 133–400 MHz |

| Bulverde | Wireless MMX, Wireless SpeedStep added | 32 KB/32 KB, MMU | 312–624 MHz | ||

| Monahans |

Wireless MMX2 added | 32 KB/32 KB (L1), optional L2 cache up to 512 KB, MMU | up to 1.25 GHz | ||

| Snapdragon | ARMv7-A | Scorpion |

Used by some members of the Snapdragon S1, S2, and S3 families. 1 or 2 cores. ARM / Thumb / Thumb-2 / DSP / SIMD / VFPv3 FPU / NEON (128-bit wide) | 256 KB L2 per core | 2.1 DMIPS / MHz per core |

| Krait |

Used by some members of the Snapdragon S4 family. 1, 2, or 4 cores. ARM / Thumb / Thumb-2 / DSP / SIMD / VFPv4 FPU / NEON (128-bit wide) | 4 KB / 4 KB L0, 16 KB / 16 KB L1, 512 KB L2 per core | 3.3 DMIPS / MHz per core | ||

| Apple Ax | ARMv7-A | Apple Swift [32] |

Custom ARM core used in the Apple A6 and Apple A6X. 2 cores. ARM / Thumb / Thumb-2 / DSP / SIMD / VFPv4 FPU / NEON | L1: 32 kB instruction + 32 kB data, L2: 1 MB | 3.5 DMIPS / MHz Per Core |

| Family | ARM Architecture | Core | Feature | Cache (I/D), MMU | Typical MIPS @ MHz |

ARMv8 و پلتفرم 64 بیتی

در سال 2011 نسل جدید ARMv8 رسما معرفی شد و پشتیبانی از معماری 64 بیتی به آن اضافه گردید. در ARMv8 دستورات 32 بیتی برروی سیستمعامل 64 بیتی قابل اجرا هستند و در آن سیستمعاملهای 32 بیتی نیز از طریق مجازی سازی 64 بیتی اجرا میشوند. شرکتهای AMD, Micro, Brodom, Calxeda, Hisilicon, Samsung و ST Microelectronics گواهی استفاده از معماری ARMv8 را دریافت کردهاند و اعلام نمودهاند SoCهای مبتنی بر این معماری را تولید خواهند کرد. خود ARM نیز دو طراحی Cortex-A53 و Cortex-A57 را در 30 اکتبر 2012 معرفی کرد که هر دو مبتنی بر معماری ARMv8 هستند.

لینوکس که هسته اندروید نیز است به تازگی هسته اصلی سیستمعامل (Kernel) خود را بروز کرده تا از ARMv8 پشتیبانی کند. انتظار میرود در سال 2013 بسیاری از سیستم-روی-یک-چیپهای دنیا از معماری ARMv8 بهره ببرند.

چه سیستمعاملهایی از ARM پشتیبانی میکنند؟

سیستمهای Acorn: اولین کامپیوتر مبتنی بر معماری ARM، کامپیوتر شخصی Acorn بود که از سیستمعاملی به نام Arthur بهره میبرد. سیستمعاملی مبتنی بر RISC OS که از معماری ARM پشتیانی میکرد و Acorn و برخی دیگر از تولیدکنندگان از آن استفاده میکردند.

سیستمعاملهای توکار: معماری ARM از طیف وسیعی از سیستمعاملهای توکار مانند Windows CE, Windows RT, Symbian, ChibiOS/RT, FreeRTOS, eCos, Integrity, Nucleus PLUS, MicroC/OS-II, QNX, RTEMS, CoOS, BRTOS, RTXC Quadros, ThreadX, Unison Operating System, uTasker, VxWorks, MQX و OSE پشتیبانی میکند.

یونیکس: یونیکس و برخی از سیستمعاملهای مبتنی بر یونیکس مانند: Inferno, Plan 9, QNX و Solaris از ARM پشتیبانی میکنند.

لینوکس: بسیاری از توزیعهای لینوکس از ARM پشتیبانی میکنند از آن جمله میتوان به اندروید و کروم گوگل، Arch Linux، بادا سامسونگ، Debian، Fedora،OpenSuse، Ubuntu و WebOS اشاره کرد.

BSD: برخی از مشتقات BSD مانند OpenBSD و iOS و OS X اپل نیز از ARM پشتیبانی میکند.

ویندوز: معماریهای ARMv 5, 6 و 7 از ویندوز CE که در ابزارهای صنعتی و PDAها استفاده میشود، پشتیبانی میکند. ویندوز RT و ویندوز فون نیز از معماری ARMv7 پشتیبانی میکنند.

گواهی و هزینه استفاده از معماری ARM

ARM خود تولیدکننده نیمه هادی نیست و در عوض از راه صدور مجوز استفاده از طراحیهای خود، درآمد کسب میکند. گواهی استفاده از معماری ARM شرایط خاص و متنوعی را دارد و در شرایط مختلف هزینه مربوط به استفاده از آن نیز تفاوت میکند. ARM به همراه گواهینامه خود اطلاعات جامعی در مورد نحوه یکپارچگی قسمتهای مختلف با هستهها را ارائه میکند تا تولیدکنندگان به راحتی بتوانند از این معماری در سیستم-روی-یک-چیپهای خود بهره ببرند.

ARM در سال 2006 و در گزارش سالانه خود اعلام کرد که 164.1 میلیون دلار از بابت حق امتیاز یا حق اختراع، درآمد داشته که این مبلغ از بابت فروش گواهی استفاده از معماری این شرکت در 2.45 میلیارد دستگاه مبتنی بر ARM بدست آمده است. این یعنی ARM Holding بابت هر گواهی 0.067 دلار درآمد کسب نموده، اما این رقم میانگین است و براساس نسلهای مختلف و نوع هستهها متفاوت خواهد بود. مثلا هستههای قدیمی ارزانتر و معماری جدید گرانتر است.

اما در سال 2006 این شرکت از بابت گواهی استفاده از طراحی هسته پردازنده، نزدیک به 119.5 میلیون دلار درآمد بدست آورده است. در آن سال 65 پردازنده براساس معماری هسته های ARM ساخته شده بودند که به این ترتیب بابت هر گواهی پردازنده مبلغ 1.84 میلیون دلار درآمد کسب کرده است. این عدد نیز بصورت میانگین میباشد و براساس نوع و نسل هستهها متفاوت خواهد بود.

در واقع شرکت ARM Holding از معماری ARM دو نوع درآمد دارد یکی بابت استفاده از معماری این شرکت در ابزارهای مختلف که بابت هر تلفن یا تبلت یا هر ابزار دیگری مبلغی بدست میآورد و دیگری بابت هر پردازنده مبتنی بر معماری هستههای ARM نیز یک رقم نسبتا سنگین حدود 2 میلیون دلار دریافت میکند. در سال 2006 نزدیک به 60 درصد درآمد ARM از بابت حق امتیاز و 40 درصد بابت گواهی ساخت پردازنده براساس معماری ARM بوده است.

آخرین دیدگاهها